Core clock

Resources: none

The core clock runs by default at 48 MHz.

Goal

Know why the default core clock frequency of the MCXA153 is 48 MHz.

Required hardware

- None

Clocking

So far, the following for-loop has been used to create a delay:

// Delay

for(volatile int i=0; i<1000000; i++)

{}

This gave a nice visual effect, because the blinking of the LED was not too slow nor too fast. A more precise timing, however, is preferred, so let's first find out at which frequency the MCXA153 microcontroller is executing instructions.

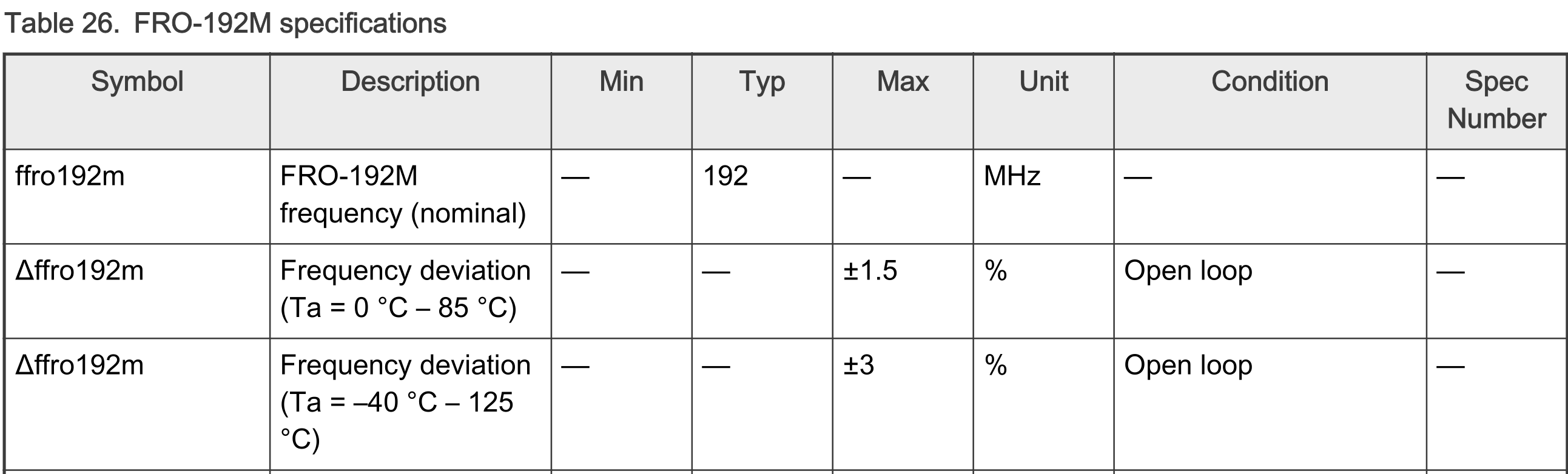

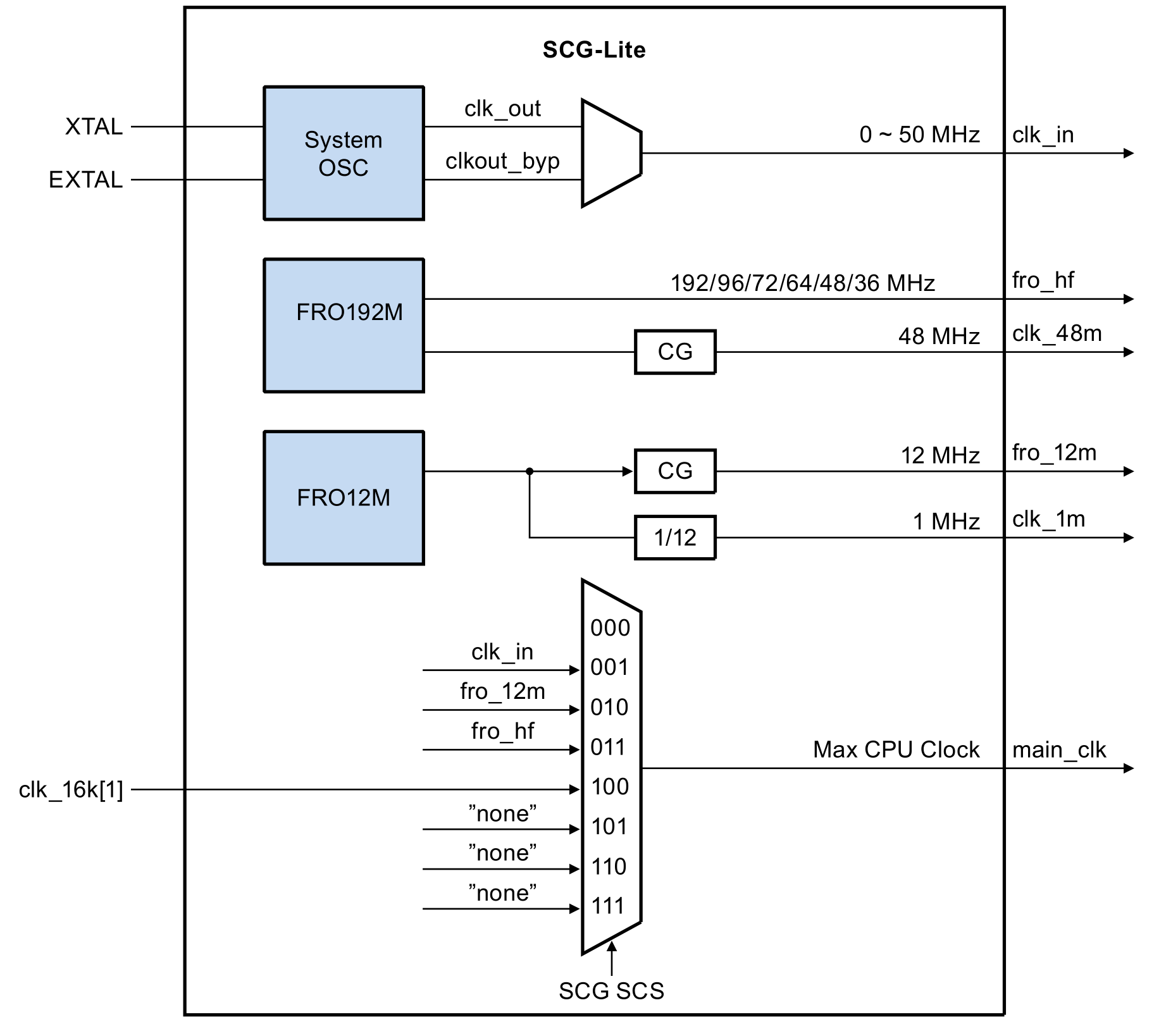

The clocking options are depicted in the following figure in chapter 21 of the reference manual.

It shows that:

- There is a clocking module called System OSC. OSC means OSCillator. This module derives a clock frequency from an externally connect XTAL oscillator. XTAL means crystal.

- There are two internal clocking modules, called FRO192M and FRO12M. FRO means Free Running Oscillator. M means MHz.

- CG means Clock Gating. This is a means to disable clock signals in order to save power. CG is enabled/disabled by writing bits in specific registers.

- The main_clk can be selected from eight inputs, however, only four are implemented. The main_clk is selected in the SCG module by the SCS bits (located in the CSR register).

The default value (after a reset) of the SCS bits in the SCG->CSR register is described in chapter 22 of the reference manual. The value of these bits is 0b011, which means the option FIRC is selected.

SCS: Returns the currently configured clock source generating the system clock.

000b - Reserved

001b - SOSC

010b - SIRC

011b - FIRC

100b - ROSC

101b-111b - Reserved

And furthermore, referring to section 22.1.3 Clock decoder ring, it shows how the clock name sources in the SCG chapter translate to names throughout the rest of the reference manual:

| SCG chapter name | Reference manual name |

|---|---|

| SOSC | clk_in |

| SIRC | fro_12m |

| FIRC | fro_hf |

| ROSC | clk_16k[1] |

So by default, the fro_hf clock is selected for the main_clk. However, the image shows that this can be one of the following frequencies: 192/96/72/64/48/36 MHz. Paragraph 21.2 states that the fro_hf default frequency is 48 MHz.

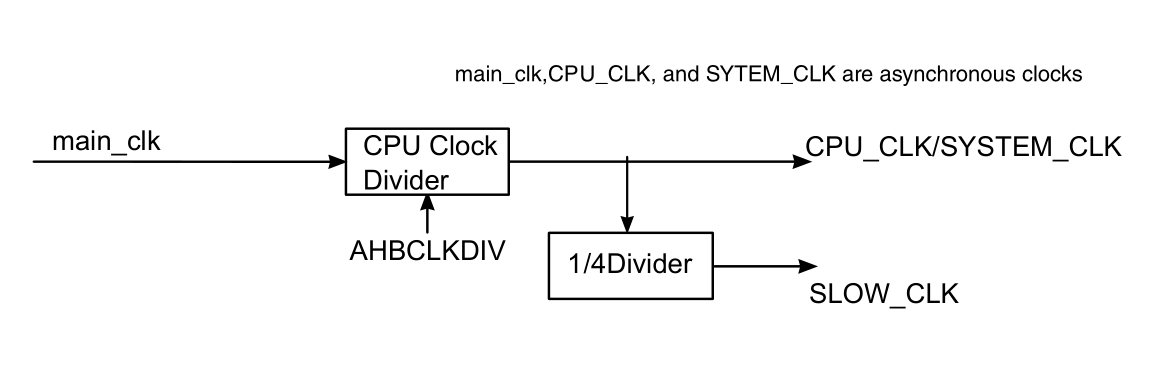

Finally, the main_clk is used to clock the CPU and rest of the system. The CPU Clock Divider, as shown in the following figure in chapter 21 of the reference manual, divides this clock. It shows that the AHBCLKDIV register is used to set the divider value.

The AHBCLKDIV register in chapter 14 of the reference manual shows that the default (reset) value of the DIV bits:

Clock divider value = (DIV + 1) = 0b00000000 + 1 = 1

So by default, the main_clk is divided by 1.

Conclusion

By default the CPU core clock runs at 48 MHz.

Or is it? Please be aware of the fact that the clock signal generated by the FRO modules have a deviation margin. This margin is specified in the datasheet. In timing critical applications, this deviation might be a problem. In such applications, an external oscillator with better precision can be connected to the XTAL and EXTAL pins.