Dit vak wordt verzorgd voor tweedejaars ESE studenten. Het vak toont de mogelijkheden van het ontwerpen van geavanceerde digitale systemen op basis van een CPLD of FPGA met de VHDL taal.

Algemeen

Alle informatie over het vak is te vinden in onderstaande download. Let op dat voor toegang van dit en de andere downloads een wachtwoord benodigd is. Vraag de de docent om dit wachtwoord .

DIG3 cursus informatie [NL]

DIG3 cursus informatie [EN]

Theorielessen

De presentaties van de theorielessen kunnen hier gevonden worden.

DIG3 presentaties

Presentatie JTAG Technologies

Practicum

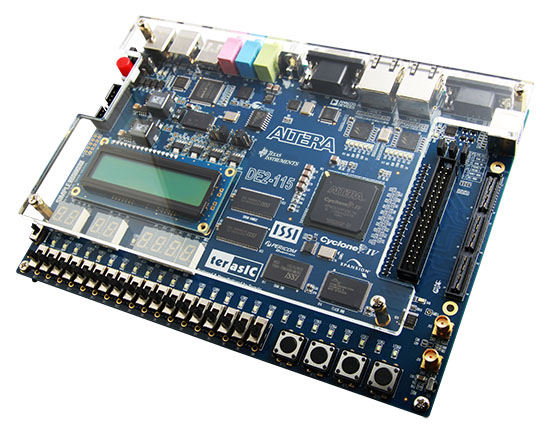

In het practicum wordt het TerAsic DE10-Lite bord op basis van de Altera MAX10 FPGA gebruikt.

Alle informatie over het practicum kan hier gevonden worden .

DIG3 practicum informatie [NL]

Dig3 practicum informatie [EN]

Het DIG3 practicum kan ook hier in de web browser bekeken worden. Voor download en toegang, zie de algemene instrukties.

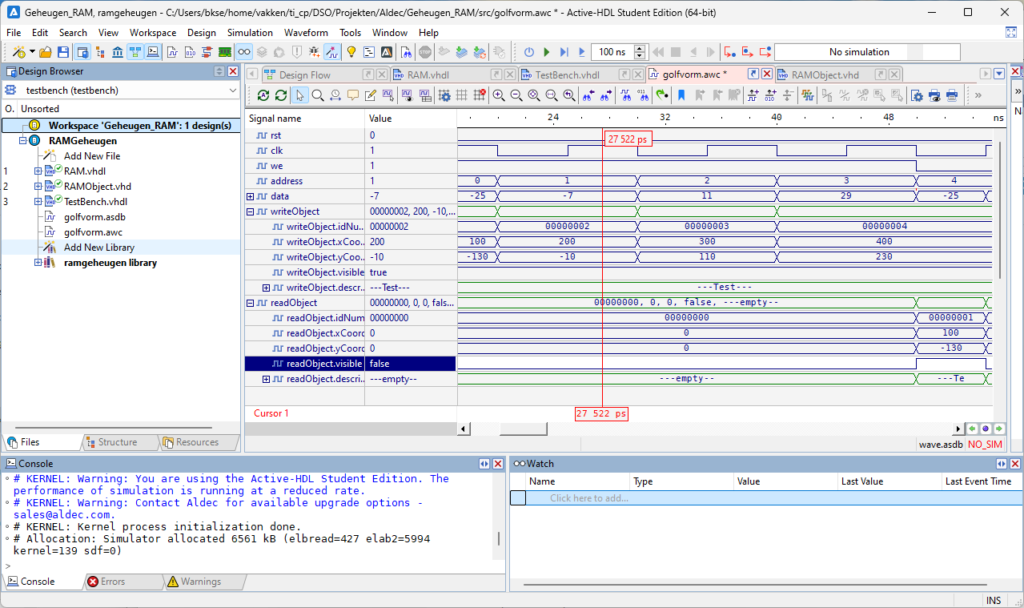

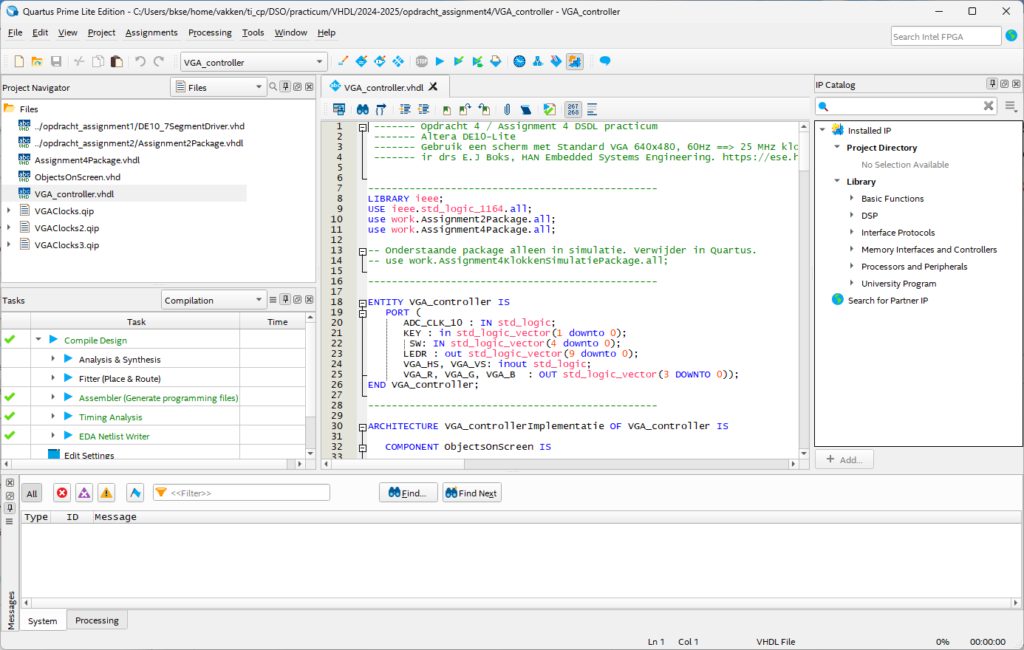

Simulator en Ontwikkelsoftware

Bij DIG3 worden de volgende pakketten gebruikt:

Voor meer informatie over het gebruik van Active-HDL is het aan te raden de video serie van Aldec te gebruiken.

Een voorbeeld staat hieronder:

Toetsing

DSD wordt getoetst op basis van twee onderdelen:

- Een theorietoets, aan het einde van het eerste blok in semester 4.

- Een practicum, bestaanden uit 5 opdrachten.

Een voorbeeldtoets kan hier worden gedownload:

DSD/DIG3 voorbeeldtoets uit 2019

Overige downloads

Informatie, handleidingen en bestanden voor het DE10-Lite board zijn hier te vinden:

TerAsic DE10-Lite board informatie

Bij het vak “Logic Circuits” hebben jullie de basis voor VHDL programmeren met Altera Quartus gehad. Ben je vergeten hoe het ook al weer ging ? De handleiding van het vak is hieronder te downloaden :

Quartus FPGA start tutorial

Deze handleiding bevat alle stappen die nodig zijn om een digitaal circuit te implementeren op het TerAsic DE0-CV bord. Deze kennis kan uiteraard ook op het DE10-Lite bord worden toegepast.